探索微世界 集成電路設(shè)計(jì)的奧秘與未來

集成電路(Integrated Circuit,簡(jiǎn)稱IC)設(shè)計(jì)是現(xiàn)代電子工業(yè)的核心與基石,它不僅是技術(shù)創(chuàng)新的驅(qū)動(dòng)力,也是信息時(shí)代得以蓬勃發(fā)展的關(guān)鍵所在。從智能手機(jī)、個(gè)人電腦到數(shù)據(jù)中心、人工智能系統(tǒng),乃至汽車電子和物聯(lián)網(wǎng)設(shè)備,幾乎每一個(gè)現(xiàn)代科技產(chǎn)品都依賴于復(fù)雜而精密的集成電路。本文將深入探討IC設(shè)計(jì)的基本概念、主要流程、關(guān)鍵技術(shù)挑戰(zhàn)以及未來發(fā)展趨勢(shì)。

一、IC設(shè)計(jì)的基本概念

IC設(shè)計(jì),簡(jiǎn)單來說,就是在一塊微小的半導(dǎo)體材料(通常是硅)上,通過一系列復(fù)雜的物理和化學(xué)過程,將數(shù)以億計(jì)的晶體管、電阻、電容等電子元件以及它們之間的互連線集成在一起,形成一個(gè)具有特定功能的電路系統(tǒng)。這個(gè)過程就像是建造一座微型的、功能齊全的“電子城市”。根據(jù)電路功能的復(fù)雜度和設(shè)計(jì)方法的不同,IC主要可以分為模擬集成電路、數(shù)字集成電路和混合信號(hào)集成電路三大類。

二、IC設(shè)計(jì)的主要流程

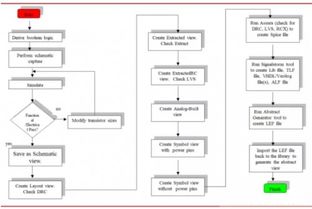

一個(gè)完整的IC設(shè)計(jì)流程是一個(gè)高度系統(tǒng)化、多階段的工程過程,通常可以分為以下幾個(gè)關(guān)鍵步驟:

- 規(guī)格定義與系統(tǒng)架構(gòu)設(shè)計(jì):這是設(shè)計(jì)的起點(diǎn)。工程師需要明確芯片需要實(shí)現(xiàn)的功能、性能指標(biāo)(如速度、功耗、面積)、工作環(huán)境以及目標(biāo)成本。在此基礎(chǔ)上,進(jìn)行高層次系統(tǒng)架構(gòu)的規(guī)劃與模塊劃分。

- 前端設(shè)計(jì)(邏輯設(shè)計(jì)):使用硬件描述語言(如Verilog或VHDL)對(duì)芯片的寄存器傳輸級(jí)(RTL)行為進(jìn)行建模和描述。這一階段主要關(guān)注功能的正確性,通過仿真驗(yàn)證邏輯是否符合規(guī)格要求。

- 功能驗(yàn)證:這是確保設(shè)計(jì)正確的關(guān)鍵環(huán)節(jié)。通過搭建復(fù)雜的測(cè)試平臺(tái),運(yùn)用仿真、形式驗(yàn)證等多種手段,對(duì)RTL設(shè)計(jì)進(jìn)行 exhaustive 的測(cè)試,以發(fā)現(xiàn)并修復(fù)邏輯錯(cuò)誤。驗(yàn)證工作通常占整個(gè)設(shè)計(jì)周期的一半以上。

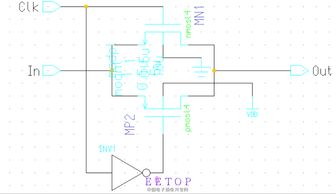

- 邏輯綜合:將RTL代碼通過電子設(shè)計(jì)自動(dòng)化(EDA)工具,轉(zhuǎn)換成由標(biāo)準(zhǔn)單元庫(kù)(如與門、或門、觸發(fā)器等)構(gòu)成的網(wǎng)表。綜合過程會(huì)優(yōu)化電路的面積、時(shí)序和功耗。

- 后端設(shè)計(jì)(物理設(shè)計(jì)):這是將邏輯網(wǎng)表轉(zhuǎn)化為實(shí)際物理版圖的過程。主要包括布局(決定每個(gè)標(biāo)準(zhǔn)單元在芯片上的位置)、布線(連接各個(gè)單元)、時(shí)鐘樹綜合(構(gòu)建全局時(shí)鐘網(wǎng)絡(luò))和物理驗(yàn)證(檢查設(shè)計(jì)規(guī)則、電氣規(guī)則等是否符合芯片制造廠的要求)。

- 流片與測(cè)試:將最終確認(rèn)的版圖數(shù)據(jù)(GDSII格式)交付給晶圓代工廠進(jìn)行制造,這個(gè)過程稱為“流片”。芯片制造出來后,需要進(jìn)行嚴(yán)格的封裝和測(cè)試,以確保其功能和性能達(dá)標(biāo)。

三、關(guān)鍵技術(shù)挑戰(zhàn)

隨著摩爾定律的持續(xù)推進(jìn),IC設(shè)計(jì)面臨著前所未有的挑戰(zhàn):

- 設(shè)計(jì)復(fù)雜性爆炸:數(shù)十億晶體管的集成使得設(shè)計(jì)、驗(yàn)證和測(cè)試的復(fù)雜度呈指數(shù)級(jí)增長(zhǎng)。

- 功耗墻:性能提升的功耗密度急劇增加,散熱和能效成為核心瓶頸。

- 時(shí)序收斂與信號(hào)完整性:在納米甚至更小工藝下,互連線延遲、串?dāng)_、電源噪聲等問題日益突出。

- 制造成本飆升:先進(jìn)工藝節(jié)點(diǎn)的研發(fā)和建廠成本極高,使得只有少數(shù)巨頭能夠參與競(jìng)爭(zhēng)。

- 人才短缺:培養(yǎng)一名經(jīng)驗(yàn)豐富的IC設(shè)計(jì)工程師需要漫長(zhǎng)的周期,全球范圍內(nèi)高端人才供不應(yīng)求。

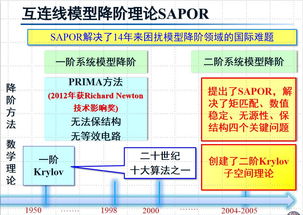

為了應(yīng)對(duì)這些挑戰(zhàn),業(yè)界正在大力發(fā)展新的設(shè)計(jì)方法學(xué)和工具,如基于高級(jí)綜合(HLS)的設(shè)計(jì)、異構(gòu)集成(Chiplet)、硅光子學(xué)、以及廣泛利用人工智能(AI)技術(shù)進(jìn)行設(shè)計(jì)空間探索、布局布線和缺陷檢測(cè)。

四、未來發(fā)展趨勢(shì)

IC設(shè)計(jì)將朝著以下幾個(gè)方向演進(jìn):

- 超越摩爾(More than Moore):在繼續(xù)追求晶體管微縮的更注重通過系統(tǒng)級(jí)封裝(SiP)、Chiplet(芯粒)等異構(gòu)集成技術(shù),將不同工藝、不同功能的芯片模塊集成在一起,實(shí)現(xiàn)更高的系統(tǒng)性能與靈活性。

- 專用領(lǐng)域架構(gòu)(DSA)的興起:針對(duì)人工智能、自動(dòng)駕駛、5G通信等特定應(yīng)用場(chǎng)景,設(shè)計(jì)高度定制化、能效比極佳的專用芯片,正成為主流趨勢(shì),打破了通用處理器(CPU)的壟斷。

- EDA與AI的深度融合:人工智能將深度賦能IC設(shè)計(jì)的各個(gè)環(huán)節(jié),從架構(gòu)探索、代碼生成到物理實(shí)現(xiàn)和驗(yàn)證,大幅提升設(shè)計(jì)自動(dòng)化水平和效率,降低對(duì)資深工程師經(jīng)驗(yàn)的依賴。

- 開源生態(tài)的構(gòu)建:類似于開源軟件,開源硬件(如RISC-V指令集架構(gòu))和開源EDA工具鏈正在興起,旨在降低設(shè)計(jì)門檻,促進(jìn)創(chuàng)新,構(gòu)建更健康、多元的產(chǎn)業(yè)生態(tài)。

- 新材料與新器件:碳納米管、二維材料(如石墨烯)、自旋電子器件等有望在未來顛覆傳統(tǒng)的硅基CMOS技術(shù),開啟全新的計(jì)算范式。

###

集成電路設(shè)計(jì)是一門融合了電子工程、計(jì)算機(jī)科學(xué)、物理學(xué)和材料科學(xué)的尖端交叉學(xué)科。它既是一門嚴(yán)謹(jǐn)?shù)墓こ炭茖W(xué),也是一門充滿創(chuàng)造力的藝術(shù)。在數(shù)字化、智能化浪潮席卷全球的今天,IC設(shè)計(jì)的重要性愈發(fā)凸顯。它不僅關(guān)乎國(guó)家科技競(jìng)爭(zhēng)力和產(chǎn)業(yè)安全,更是在微觀尺度上塑造我們未來生活面貌的核心力量。面對(duì)挑戰(zhàn),擁抱變化,持續(xù)創(chuàng)新,是IC設(shè)計(jì)領(lǐng)域永恒的主題。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.beijinghuansuogongsi.cn/product/65.html

更新時(shí)間:2026-01-23 13:21:18