模擬CMOS集成電路設(shè)計的核心要義與實踐路徑

模擬CMOS集成電路設(shè)計是微電子領(lǐng)域的技術(shù)基石,它專注于利用互補(bǔ)金屬氧化物半導(dǎo)體(CMOS)工藝,設(shè)計并實現(xiàn)能夠處理連續(xù)時間信號的電路與系統(tǒng)。與數(shù)字電路處理離散的0和1信號不同,模擬電路直接處理如電壓、電流、溫度、聲音等現(xiàn)實世界的連續(xù)物理量,其設(shè)計更依賴于對器件物理特性、電路拓?fù)浜凸に嚻畹纳羁汤斫狻?/p>

模擬CMOS設(shè)計的核心在于處理幾個永恒的矛盾:性能、功耗、面積和成本之間的權(quán)衡。設(shè)計師必須在給定的工藝節(jié)點下,通過精巧的電路架構(gòu)和嚴(yán)謹(jǐn)?shù)姆抡鎯?yōu)化,達(dá)成特定應(yīng)用(如數(shù)據(jù)轉(zhuǎn)換器、射頻前端、電源管理、傳感器接口等)所要求的增益、帶寬、噪聲、線性度和功耗指標(biāo)。

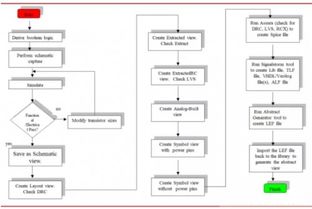

設(shè)計流程通常始于系統(tǒng)級指標(biāo)分解,確定整體架構(gòu)(如運放類型、濾波器結(jié)構(gòu))。隨后進(jìn)入晶體管級設(shè)計,這是設(shè)計的靈魂所在。設(shè)計師需深入分析MOSFET在亞微米乃至納米尺度下的行為——包括跨導(dǎo)、輸出阻抗、寄生電容、短溝道效應(yīng)以及工藝角(Process Corner)和失配(Mismatch)的影響。利用小信號模型進(jìn)行手工計算,以建立對電路行為的直觀洞察,再借助SPICE類工具(如Cadence Spectre)進(jìn)行深入的直流、交流、瞬態(tài)及噪聲仿真,反復(fù)迭代優(yōu)化器件尺寸和偏置點。

版圖設(shè)計是模擬設(shè)計成敗的關(guān)鍵環(huán)節(jié)。模擬版圖遠(yuǎn)非簡單的連線,它需要精心規(guī)劃器件匹配、考慮寄生效應(yīng)、利用共質(zhì)心等對稱結(jié)構(gòu)抵消梯度誤差、添加保護(hù)環(huán)(Guard Ring)以隔離噪聲、并遵循特定的布線規(guī)則以確保信號完整性。版圖完成后必須進(jìn)行寄生參數(shù)提取和后仿真,以驗證實際性能是否與原理圖設(shè)計相符。

隨著工藝尺寸不斷縮小,電源電壓降低,模擬設(shè)計面臨巨大挑戰(zhàn)。器件本征增益下降,溝道長度調(diào)制等二階效應(yīng)愈發(fā)顯著,設(shè)計難度劇增。這促使了新技術(shù)的發(fā)展,如使用數(shù)字輔助校準(zhǔn)技術(shù)來補(bǔ)償模擬電路的不足,以及模擬-數(shù)字混合設(shè)計方法的深度融合。

模擬CMOS集成電路設(shè)計是一門融合了深厚理論、豐富經(jīng)驗和藝術(shù)直覺的學(xué)科。它要求設(shè)計者既要有扎實的半導(dǎo)體物理和電路理論基礎(chǔ),又要有面對復(fù)雜非線性問題和工藝不確定性的工程實踐能力。在萬物互聯(lián)的智能時代,作為連接物理世界與數(shù)字世界的橋梁,高性能、低功耗的模擬電路設(shè)計將繼續(xù)扮演不可或缺的角色,驅(qū)動著從消費電子到汽車、醫(yī)療、工業(yè)等各領(lǐng)域的創(chuàng)新。

如若轉(zhuǎn)載,請注明出處:http://www.beijinghuansuogongsi.cn/product/61.html

更新時間:2026-01-23 20:24:25