數字集成電路版圖設計 附錄與持續補充

數字集成電路(IC)版圖設計是現代電子系統設計中的關鍵環節,它涉及將邏輯電路轉化為物理布局,確保芯片性能、功耗和可靠性的優化。隨著工藝技術的不斷進步,版圖設計方法也在持續演進,本附錄旨在補充相關知識,幫助設計者應對日益復雜的集成電路設計挑戰。

1. 版圖設計基礎

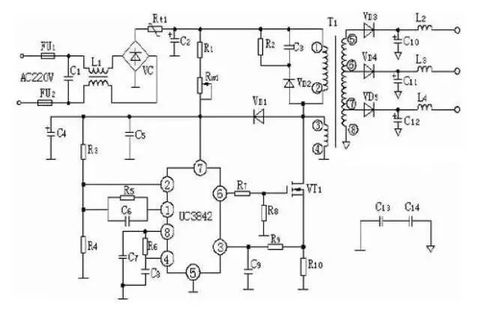

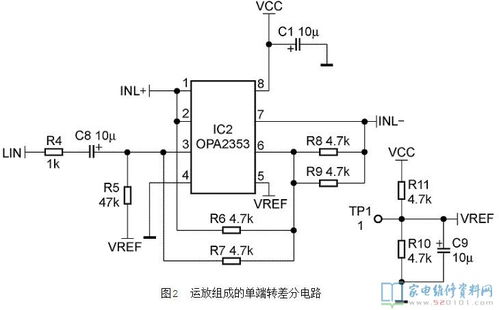

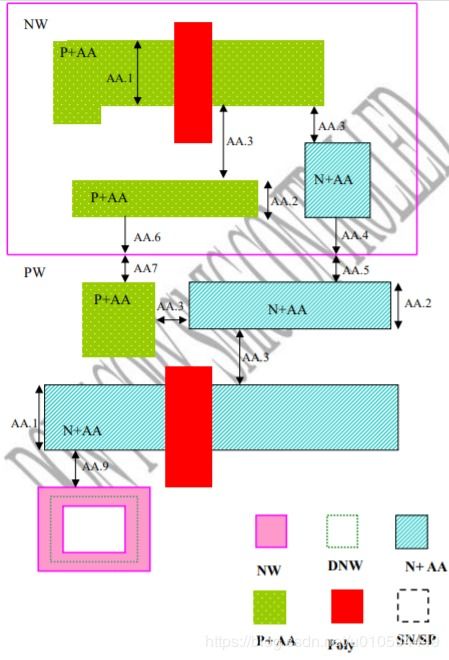

版圖設計是集成電路物理設計的核心,它定義了晶體管、互連和其他組件的幾何形狀和位置。設計者需遵循設計規則(DRC)以確保制造可行性,同時考慮電氣規則(ERC)和布局與原理圖一致性(LVS)。關鍵步驟包括:

- 布局規劃:確定功能塊的位置和大小,優化芯片面積和布線。

- 布線:使用金屬層連接組件,最小化延遲和串擾。

- 驗證:通過仿真和檢查工具確保設計符合規范。

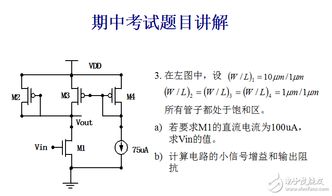

2. 先進工藝下的挑戰

隨著工藝節點縮小至納米級(如7nm、5nm),版圖設計面臨新問題:

- 寄生效應:互連電阻和電容增加,導致信號完整性問題。

- 功耗管理:需集成功耗優化技術,如電源門控和多電壓域。

- 可制造性設計(DFM):考慮工藝變異,采用冗余設計和光刻優化。

3. 持續補充與學習資源

集成電路設計是一個動態領域,設計者應持續更新知識:

- EDA工具:掌握Cadence、Synopsys等工具的最新功能。

- 開放資源:參考IEEE論文、開源項目(如OpenROAD)和行業標準。

- 實踐項目:通過實際設計案例提升技能,例如參與芯片設計競賽。

4. 未來趨勢

人工智能和自動化正重塑版圖設計,機器學習算法可用于布局優化和缺陷預測。3D集成電路和異質集成將推動版圖方法創新。

數字集成電路版圖設計要求設計者具備扎實的基礎和持續學習能力。本附錄將不定期更新,以反映技術進展,助力設計者實現高效、可靠的芯片設計。

如若轉載,請注明出處:http://www.beijinghuansuogongsi.cn/product/20.html

更新時間:2026-01-23 18:57:13